For:billk Printed on:Tue, May 18, 1999 16:18:14 From book:lasi ers Document:cover page Last saved on:Tue, May 18, 1999 16:08:55 Document:TOC Last saved on: Tue, May 18, 1999 16:11:27 Document:LOT Last saved on: Tue, May 18, 1999 16:11:25 Document:LOF Last saved on: Tue, May 18, 1999 16:11:25 **Document:**intro Last saved on:Wed, Mar 17, 1999 16:18:18 **Document:overview** Last saved on:Wed, Mar 17, 1999 16:20:32 Document:scsi Last saved on:Wed, Mar 17, 1999 16:25:23 Document:lan Last saved on:Wed, Mar 17, 1999 16:32:40 **Document:Parallel** Last saved on:Wed, Mar 17, 1999 16:52:13 Document:audio Last saved on:Wed, Mar 17, 1999 17:30:43 **Document:Serial** Last saved on:Wed, Mar 17, 1999 17:33:39 ( ...)

### Notice

The information contained in this document is subject to change without notice.

HEWLETT–PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THE MATERIAL. INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MER-CHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Hewlett–Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with furnishing, performance, or use of this material.

Hewlett–Packard sassumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett–Packard.

This document contains proprietary information that is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of the Hewlett–Packard Company.

Copyright © 1992–1999 by HEWLETT–PACKARD COMPANY All Rights Reserved.

| 712 I/O Subsystem ERS Rev 1.0 | Dwg No. A-A2263-66510-31 | Page 2 of 116 |

|-------------------------------|--------------------------|---------------|

|                               |                          |               |

| 3 Introduction                       | 1  |

|--------------------------------------|----|

| 3.1 Objectives                       | 1  |

| 3.2 Feature Summary                  |    |

| 3.3 Design Team                      |    |

| č                                    |    |

| 4 Overview                           | 3  |

| 4.1 Functional Organization          | 3  |

| 4.2 Personality Card                 |    |

| 4.2.1 Lasi Configurability           | 4  |

| 4.3 Telephone Support                |    |

|                                      |    |

| 5 SCSI                               | 5  |

| 5.1 Introduction                     | 5  |

| 5.2 Overview                         | 5  |

| 5.3 Features                         | 5  |

| 5.4 Signal Definitions               | 6  |

| 5.5 SCSI-2 Fast Single-Ended Support |    |

| 5.6 SCSI-2 Fast Differential Support |    |

| 5.7 Clock Rates                      |    |

| 5.8 NCR 710 Mode Bits                |    |

| 5.9 NCR 710 Revision Code            |    |

| 5.10 Interrupts                      |    |

| 5.11 Register Set                    |    |

| 5.11.1 SCSI Reset Register           |    |

| 5.11.2 NCR 710 Internal Registers    |    |

| 6                                    |    |

| 6 LAN                                | 11 |

| 6.1 Introduction                     | 11 |

| 6.2 References                       | 11 |

| 6.3 Nomenclature and Conventions     |    |

| 6.4 Overview                         |    |

| 6.5 Transaction Types                |    |

| 6.5.1 Channel Attention              |    |

| 6.5.2 Port Access                    |    |

| 6.6 Reset                            | 10 |

| 6.6.1 Consequences                   |    |

| 6.6.1.1 Hardware Reset               |    |

| 6.6.1.2 CPU Port Reset               |    |

| 6.6.1.3 Software Reset               |    |

| 6.6.2 Protocol                       |    |

| 6.6.2.1 Hardware Reset               |    |

| 6.6.2.2 CPU Port Reset               |    |

| 6.6.2.3 Software Reset               |    |

| 6.7 Interrupts                       |    |

| 6.8 Programming Considerations       |    |

| 6.8.1 Endian Mode                    |    |

| 6.8.2 Bus Size                       |    |

| 6.8.3 System Configuration Pointer   |    |

| 6.8.4 Sysbus Byte                    |    |

| 6.8.4.1 Mode                         |    |

| 0.0. <del>.</del> .1 MIOUG           | 10 |

| 6.8.4.2 Bus Throttle and Arbitration                  | 15 |

|-------------------------------------------------------|----|

| 6.8.4.3 Locked Cycles                                 | 16 |

| 6.8.4.4 Interrupt Pin Polarity                        | 16 |

| 6.8.4.5 Channel Switch Algorithm                      | 16 |

| 6.8.5 Performance Considerations                      | 16 |

| 6.8.5.1 FIFO Vector                                   | 16 |

| 6.8.5.2 Memory Organization                           | 16 |

| 6.9 Station Nodal Address                             | 16 |

| 6.10 LAN Memory Map                                   | 16 |

| 5 1                                                   |    |

| Parallel Interface                                    | 19 |

| 7.1 Introduction                                      | 19 |

| 7.2 Overview                                          | 19 |

| 7.3 Features                                          | 19 |

| 7.4 Addressing                                        | 19 |

| 7.5 Power Up Reset                                    | 20 |

| 7.6 Quick Reference for Parallel Slave Registers      | 21 |

| 7.7 Slave Register Descriptions                       | 21 |

| 7.7.1 Directed Master Reset (Address slv+0x000)       | 21 |

| 7.7.2 Write/Read Data (Address slv+0x800)             | 22 |

| 7.7.3 Parallel Port Status (Address slv+0x801)        | 22 |

| 7.7.4 Parallel Device Control (Address slv+0x802)     | 23 |

| 7.7.5 Mode Control (Address slv+ $0.804$ )            | 23 |

| 7.7.6 IE Control/Interrupt Status (Address slv+0x805) | 25 |

| 7.7.7 Timing Delay Counter 0 (Address slv+0x806)      | 25 |

| 7.7.8 Timing Delay Counter 1 (Address slv+0x807)      | 26 |

| 7.8 Parallel Port DMA Controller                      | 27 |

| 7.9 Parallel DMA Register Map                         | 27 |

| 7.10 How Parallel Port DMA Works                      | 27 |

| 7.11 Parity Errors and Bus Timeouts                   | 28 |

| 7.12 Detailed Register Descriptions                   | 28 |

| 7.12.1 Parallel DMA Reset Register                    | 28 |

| 7.12.2 Current Address Registers                      | 28 |

| 7.12.3 Byte Count Registers                           | 29 |

| 7.12.4 DMA Status register                            | 30 |

| 7.12.5 DMA Write single mask bit                      | 30 |

| 7.12.6 DMA Mode register                              | 30 |

| 7.12.7 DMA Interrupt Logging Register                 | 31 |

| 7.12.8 DMA Mask Register                              | 32 |

| 7.12.9 FIFO Limit Register                            | 32 |

| 7.12.10 DMA Clear byte pointer                        | 32 |

| 7.12.11 DMA Master Clear                              | 32 |

| 7.12.12 Clear Mask register                           | 32 |

| 7.13 Typical DMA Sequence                             | 33 |

| 7.14 EISA Compatibility                               | 34 |

| 7.15 Testing                                          | 34 |

| 7.16 Timing Examples                                  | 35 |

| 7.10 Immig Examples                                   | 5. |

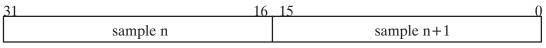

| Audio/Telephone                                       | 37 |

| 8.1 Introduction                                      | 37 |

| 8.1.1 Audio Description                               | 37 |

|                                                       | 51 |

| 8.       | 1.2 Telephony Description                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------|

| 8.       | 2 CHI Communication                                                                                             |

|          | .3 Harmony Architecture                                                                                         |

|          | .4 Audio Software Interface                                                                                     |

|          | .4.1 Base Offset                                                                                                |

|          | .4.2 ID register (Address: 0x000)                                                                               |

|          | .4.3 Initializing the CODEC                                                                                     |

|          | .4.4 Playback and Recording                                                                                     |

|          | .4.5 Gain Control                                                                                               |

|          | .4.6 Over-range Indication                                                                                      |

|          |                                                                                                                 |

|          | 4.7 PIO register                                                                                                |

|          | 4.8 DIAG register                                                                                               |

|          | 5 TTY Software Interface                                                                                        |

|          | .5.1 Receive Buffer and Transmit Hold Register                                                                  |

| 8.       | .5.2 Interrupt Enable Register                                                                                  |

|          | .5.3 Interrupt Identification Register                                                                          |

|          | .5.4 Fifo Control Register                                                                                      |

|          | .5.5 Line Control Register                                                                                      |

|          | .5.6 Modem Control Register                                                                                     |

| 8.       | .5.7 Line Status Register                                                                                       |

| 8.       | .5.8 Modem Status Register                                                                                      |

| 8.       | .5.9 Divisor Latch Register LSB                                                                                 |

|          | .5.10 Divisor Latch Register MSB                                                                                |

|          | .5.11 Telephony Information Byte                                                                                |

|          | .6 ISDN Interface                                                                                               |

| 9.<br>9. | .1 Introduction         .2 Feature Summary         .3 Register Definitions         .4 Differences from NS16550A |

| ).       |                                                                                                                 |

| 10 R     | eal-Time Clock                                                                                                  |

| 1        | 0.1 Introduction                                                                                                |

| 10       | 0.2 Feature Summary                                                                                             |

|          | 0.3 Register Definition                                                                                         |

|          |                                                                                                                 |

|          | S2 Interface for keyboard/mouse                                                                                 |

|          | ntroduction                                                                                                     |

|          | Legisters                                                                                                       |

|          | D Register                                                                                                      |

|          | leset Register                                                                                                  |

|          | Cevdata Register                                                                                                |

|          | Imtdata Register                                                                                                |

|          | Control Register (R/W)                                                                                          |

| S        | tatus Register (Read only)                                                                                      |

| A        | ddressing                                                                                                       |

|          | nterrupt processing                                                                                             |

|          | ïming                                                                                                           |

| 11 D     | CElement                                                                                                        |

|          | C Floppy                                                                                                        |

| 12       | 2.1 Introduction                                                                                                |

| 12.2 DMA Operation                         | 71 |

|--------------------------------------------|----|

| 12.2.1 Servicing the Circular Buffer       | 72 |

| 12.3 PC Floppy Registers                   | 72 |

| 12.3.1 FDC Registers                       | 72 |

|                                            |    |

| 1 Flash Eprom                              | 75 |

| 1.1 Overview                               | 75 |

| 1.2 Memory Map                             | 75 |

| 1.3 Performance                            | 76 |

| 1.3.1 Reading Data                         | 76 |

| 1.3.2 Writing Data                         | 76 |

|                                            |    |

| 13 Power System Support                    | 77 |

| 13.1 Overview                              | 77 |

| 13.2 Reset                                 | 77 |

| 13.2.1 RESETL Configurability              | 77 |

| 13.2.2 I/O Reset                           | 77 |

| 13.3 Smart Power Switch                    | 78 |

| 13.4 LED Control                           | 79 |

|                                            |    |

| 2 Miscellaneous Registers                  | 81 |

| 2.1 I/O Configuration Registers            | 81 |

| 2.2 Setting the Registers                  | 81 |

| 2.2.1 Primary I/O Configuration Register   | 81 |

| 2.2.2 Secondary I/O Configuration Register | 82 |

| 2.3 Error Logging Register                 | 82 |

| 2.4 Lasi Version Control Register          | 83 |

|                                            |    |

| 14 Interrupts                              | 85 |

| 14.1 Overview                              | 85 |

| 14.2 Register Definitions                  | 85 |

| 14.3 Interrupt Operation                   | 86 |

| 14.4 Interrupt Register Bit Assignments    | 86 |

| 14.5 Error Handling                        | 87 |

|                                            |    |

| 15 GSC Interface                           | 89 |

| 15.1 Interface Overview                    | 89 |

| 15.2 Connection Control Path               | 89 |

| 15.2.1 Control Simplification Ideas        | 89 |

| 15.3 Lasi's Data /Address Path             | 89 |

| 15.4 LASI GSC Behavior Summary             | 90 |

|                                            |    |

| 16 Arbitration                             | 91 |

| 16.1 712 Arbitration Overview              | 91 |

| 16.2 Arbitration Mask Register             | 91 |

| 16.3 Disabling the Arbitration Controller  | 92 |

|                                            |    |

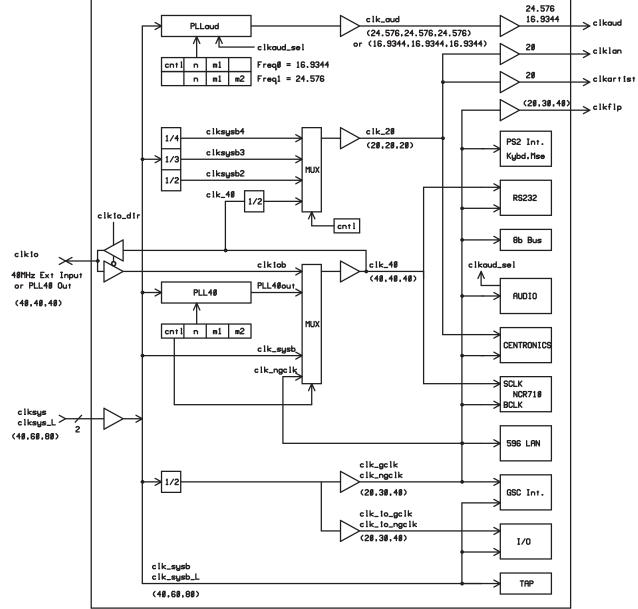

| 17 Clocks                                  | 93 |

| Introduction                               | 93 |

| Overview                                   | 95 |

| Appendix B: 712 System Memory Map                        | 105                                                                                                                                                                                                                      |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix A: 712 I/O Memory Map                           | 99                                                                                                                                                                                                                       |

|                                                          | 98                                                                                                                                                                                                                       |

| PLL Coefficients                                         | 97                                                                                                                                                                                                                       |

| 17.1.3 Register: clk_aud1 = 24.576 MHz Target Frequency  | 97                                                                                                                                                                                                                       |

| 17.1.2 Register: clk_aud0 = 16.9344 MHz Target Frequency | 97                                                                                                                                                                                                                       |

| 17.1.1 Register: clk_20                                  | 97                                                                                                                                                                                                                       |

| 17.1 Register: clk_40                                    | 96                                                                                                                                                                                                                       |

| Registers                                                | 96                                                                                                                                                                                                                       |

|                                                          | 17.1.1 Register: clk_20         17.1.2 Register: clk_aud0 = 16.9344 MHz Target Frequency         17.1.3 Register: clk_aud1 = 24.576 MHz Target Frequency         PLL Coefficients         Appendix A: 712 I/O Memory Map |

| Table 4. SCSI Register Set                                   | 8   |

|--------------------------------------------------------------|-----|

| Table 5. RS232 Register Definitions                          | 64  |

| Table 6. PS2 Interface Registers                             | 67  |

| Table 7. PS2 ID Register                                     | 67  |

| Table 8. PS2 Control Register                                | 69  |

| Table 9. PS2 Status Register                                 | 69  |

| Table 10. Floppy Disk Controller Registers                   | 72  |

| Table 11. Floppy Registers                                   | 73  |

| Table 12. DMA Registers                                      | 73  |

| Table 13. Floppy Control Register bit Definition             | 73  |

| Table 14. Floppy Status Register bit Definition              | 73  |

| Table 15. Floppy DMA Address Register bit Definition         | 74  |

| Table 16. Floppy DMA Enable Register bit Definition          | 74  |

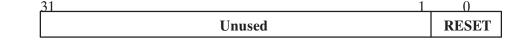

| Table 17. I/O Reset Register                                 | 78  |

| Table 18. Power Control Register bit Definition              | 79  |

| Table 1. I/O Configuration Primary Register Bit Definition   | 82  |

| Table 2. I/O Configuration Secondary Register Bit Definition | 82  |

| Table 3. Error Logging Resister                              | 83  |

| Table 19. Interrupt Registers                                | 86  |

| Table 20. Interrupt Control Register Bit Definition          | 86  |

| Table 21. IPR, IMR, and IRR Bit Definition                   | 87  |

| Table 22. 712 Bus Masters                                    | 91  |

| Table 23. Arbitration Mask Register                          | 92  |

| Table 24. LASI Internal and External Clocks                  | 95  |

| Table 25. LASI PLL Coefficients                              | 98  |

| Table 26. Address offsets for712 I/O                         | 104 |

| Table 27. Lasi Base Addresses                                | 104 |

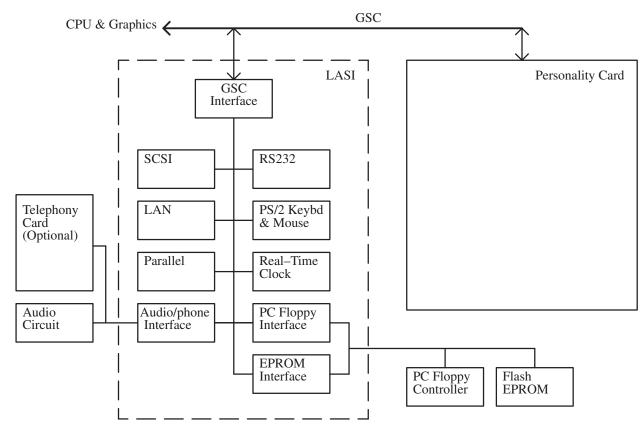

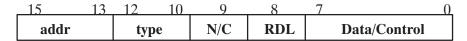

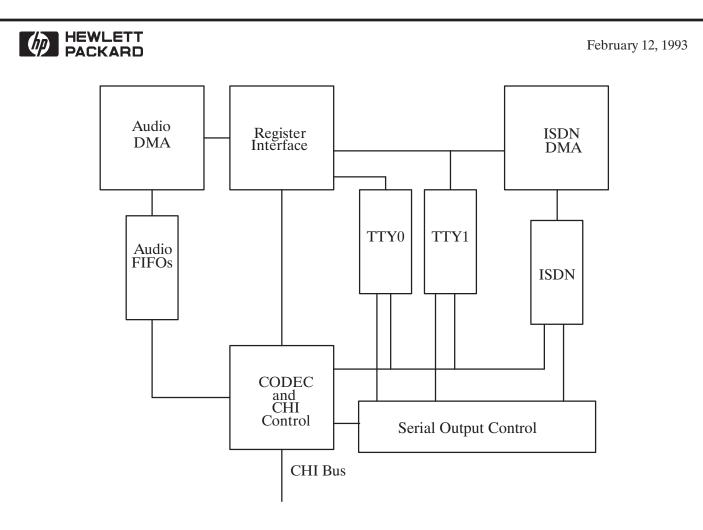

| Figure 2. I/O Subsystem Block Diagram | 3  |

|---------------------------------------|----|

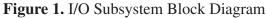

| Figure 3. Parallel Data Timing        | 26 |

| Figure 4. Harmony Block Diagram       | 43 |

| Figure 5. Floppy DMA Address Register | 71 |

| Figure 1. Flash EPROM Memory Map      | 75 |

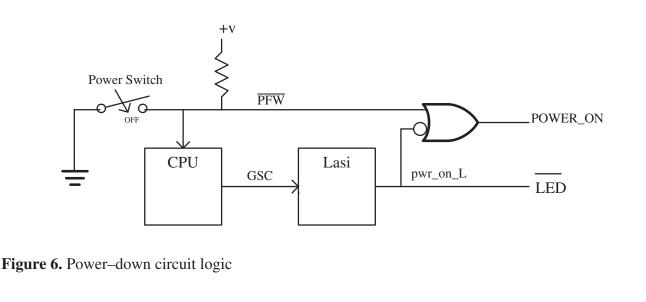

| Figure 6. Power-down circuit logic    | 78 |

| Figure 7. LASI Clock Diagram          |    |

|                                       | 94 |

## **1 INTRODUCTION**

## 1.1 Objectives

The primary objective for the 712 I/O subsystem is to provide a core set of I/O functionality that is consistent with the cost and performance goals of the 712 box.

The primary objective for this document is to describe the software interface to 712 I/O with enough detail to allow driver development. This document (along with referenced documents) contains enough detail to ascertain the intended functionality of each block on the Lasi chip down to the register level.

This version of the document (1.1) should contain an accurate description of the 712 I/O Subsystem functionality for Lasi 1.0.

## **1.2 Feature Summary**

The following is a list of the features of the 712 I/O Subsystem:

- SCSI (DMA)

- LAN (DMA)

- Parallel Printer Interface (DMA)

- CD quality Stereo Audio (DMA)

- serial RS232 port

- PS/2 Keyboard and mouse interface

- Real Time Clock

- 256K bytes of Flash EPROM

- Power system support

- PC floppy disk drive (DMA–optional)

- telephone interfaces (optional)

- Personality Card (optional)

## 1.3 Design Team

<Deleted from public version of document>

## **2 OVERVIEW**

HEWLETT PACKARD

## 2.1 Functional Organization

The heart and soul of the 712 I/O Subsystem is the Lasi chip. The vast majority of the I/O functionality in 712 is either completely implemented on Lasi or accessed through Lasi. The one exception to this is the optional personality card which has its own GSC interface. The personality card is intended for IBM Token Ring or an additional I/O device implemented with a second Lasi chip. The Block diagram in figure 1 shows the organization of the 712 I/O Subsystem.

### 2.2 Personality Card

The personality card allows some flexibility in Gecko I/O while maintaining the lowest possible factory cost for the base system. The current plan is to have two different flavors of the personality card. The first card would use an ASIC (Wax) to interface GSC to the TI Token Ring chip set. The second

| 712 I/O Subsystem ERS Rev 1.0 | Dwg No. A-A2263-66510-31 | Page 3 of 144 |

|-------------------------------|--------------------------|---------------|

| ,, ,                          |                          |               |

would use another Lasi chip to implement a second copy of one or more of the I/O devices implemented in Lasi.

#### 2.2.1 Lasi Configurability

The Lasi chip has four configuration bits that allow enough flexibility to use a second Lasi on the personality card. The SPACE[1:0] bits control which of four possible base addresses are decoded by Lasi. The RESET\_SLAVE bit allows to another GSC device to drive the RESETL signal. The ARB\_SLAVE bit allows another device control GSC arbitration. These bits are all set during reset by pulling configuration pins either high or low through a resistor. This configuration flexibility allows more than one Lasi to reside on the same GSC. It also provides the flexibility required to make Lasi useable by some non–Gecko systems. The configuration registers in the second Lasi can be read by PDC to identify which of Lasi's I/O functionality can be used (ie. have connectors) on the second Lasi chip.

## 2.3 Telephone Support

Gecko supports an optional board that provides simultaneous access to two telephone lines. One can be used for voice, and the other for either voice or data. This functionality is provided on a separate board to reduce the cost of the base configuration and to accommodate the differences in international phone systems. This board has a dedicated interface that is not intended to support any other functionality.

| 712 I/O Subsystem ERS Rev 1.0 | Dwg No. A-A2263-66510-31 | Page 4 of 144 |

|-------------------------------|--------------------------|---------------|

|-------------------------------|--------------------------|---------------|

## 3 SCSI

## **3.1 Introduction**

SCSI (Small Computer System Interface) is a system level interface bus used to connect disc drives, tape drives, and other I/O devices to a computer system. Numerous workstations today support this bus standard, as SCSI is becoming the defacto disc interface standard. SCSI–1 consists of 8 bits of data at up to a 4 MB/sec for synchronous transfer rate. SCSI–2, however, allows up to a 10 MB/sec transfer rate with an 8 bit bus, up to 20 MB/sec with a 16 bit bus and up to 40 MB/sec with an extended 32 bit data bus.

## 3.2 Overview

The 712 I/O subsystem will support SCSI–2 specification and HPCS (HP Common SCSI) command set. However, the 712 I/O subsystem will only support the 8 bit data bus SCSI configuration and will support neither the 16 nor 32 bit data bus configuration.

The 712 built–in SCSI–2 port is implemented using a NCR 53C710 SCSI I/O Processor macrocell inside the LASI chip, referred to as NCR 710 Macrocell. The NCR 710 Macrocell will be configured in 8 bit single–ended SCSI–2 mode and, with a 40MHz SCSI clock, can transfer data at a maximum data rate of 5 MB/sec on the SCSI bus.

The NCR 53C710 Host Bus interface contains a 32b DMA engine which supports burst transfer rates up to 66 MB/sec, and a "script processor," which fetches its own commands and performs SCSI transactions with minimal host processor intervention.

For a detailed description, refer to the NCR 53C710 SCSI I/O Processor Data Manual rev 1.0.

## 3.3 Features

- Full NCR 710 SCSI and "SCRIPT" Compatibility

- SCSI-2 Single-Ended direct connection without external transceivers

- 40 MHz SCSI Clock (SCLK)

- Supports system frequencies up to 66MHz

- Snoop bit 1 SC[1] is connected for run time interrupt

#### February 12, 1993

##

## 3.4 Signal Definitions

LASI supports the 8 bit Single–Ended SCSI–2 bus signals: scsd\_L[7:0], scsdbp\_L, scscd\_L, scsio\_L, scsmsg\_L, scsreq\_L, scsack\_L, scsbsy\_L, scssel\_L, scsatn\_L, and scsrst\_L.

The NCR 710 Differential Support Lines (14 signals) are not supported on the GECKO built–in LASI pins.

Please see Appendix B: LASI Pin Definitions for detailed LASI signal list and LASI naming.

## 3.5 SCSI-2 Fast Single-Ended Support

The NCR 710 macrocell itself is capable of data transfer rates up to 10 MB/sec, however, LASI will not support SCSI–2 Single–Ended timing at greater than a 5 MB/sec transfer rate. It may be possible for very restricted configurations to run faster, but we have no plans to characterize or ensure this operation.

## 3.6 SCSI-2 Fast Differential Support

The NCR 710 Differential Support Lines (14 signals) are not supported on the GECKO built–in LASI pins. However, the NCR 710 Macrocell will contain the internal circuitry to generate these signals for future macrocell applications. The NCR 710 Macrocell itself is capable of data transfer rates up to 10 MB/sec in 8 bit Fast Differential mode. The rest of LASI and the GSC will be designed to support 10 MB/sec data rates to allow for future LASI variants.

## 3.7 Clock Rates

Unlike the NCR 53C700, the 53C710 has separate clocks for the Host Bus Interface and the SCSI Bus Interface. The host–side Bus Clock (BCLK) operates up to 33MHz. Lasi has a fixed 1/2 ratio between its internal C710's BCLK and the system clock, allowing system clock frequencies up to 66 MHz.

The SCSI Clock (SCLK) will operate at a fixed 40MHz.

## 3.8 NCR 710 Mode Bits

The NCR 710 Bus Mode Select (BS\_L) signal will be hardwired to logic 0 (Synchronous (68040–like) host bus mode). The Big/Little Endian Select (BIG\_LIT\_L) signal will be hardwired to logic 1 (Big endian byte order).

## 3.9 NCR 710 Revision Code

The LASI chip NCR 710 Macrocell implementation is based on NCR 53C710 Rev. D (Rev. 4). The chip revision field reported by the chip should be "2".

## 3.10 Interrupts

LASI implements the Running Interrupt (or Interrupt–on–the–Fly Interrupt) in addition to the normal NCR 710 IRQ line. The logic equation for the NCR 710 Macrocell interrupt is:

$\label{eq:NCR710_IRQ_L ==> IPR[9] ("normal" interrupt) \\ NCR710_SC[1]_L ==> IPR[21] ( Interrupt-on-the-Fly ) \\$

IRQ is enabled through the NCR710 SIEN register.

## 3.11 Register Set

The SCSI Register Set as viewed from the GSC Bus is shown in Table 1.

All addresses in the memory map are specified relative to the relocatable Lasi base address. Byte addresses are "Big Endian" byte numbering mode (Byte 0 is most significant and on the left). Note that this byte numbering is **NOT** consistent with the "Little Endian" byte addressing used in the EISA SCSI Host Adapter card (25525A) using the NCR 53C710. Bit numbering is "Little Endian" (bit 0 is least significant and on the right).

The GSC may access registers using byte or 32 bit word addresses. LASI does not require byte swapping for registers which have more than one byte; the ASP chip used in the 720/730/750 systems did.

#### Table 1. SCSI Register Set

HEWLETT PACKARD

| Address (Hex) | 31            | Bit Numbering |         |        |       | 0      |       |

|---------------|---------------|---------------|---------|--------|-------|--------|-------|

|               | Byte 0        | Byte 1        |         | Byte 2 |       | Byte 3 |       |

| 000           | SCSI Reset (W | 7)            |         |        |       |        |       |

| 004           |               | RESE          | RVED    | 1      |       | 1      |       |

| :             |               |               |         |        |       |        |       |

| 0FF           |               | RESE          | RVED    |        |       |        |       |

| 100           | SIEN (R/W     | ) SDID        | (R/W)   | SCNTL1 | (R/W) | SCNTL0 | (R/W) |

| 104           | SOCL (R/W     | ) SODL        | (R/W)   | SXFER  | (R/W) | SCID   | (R/W) |

| 108           | SBCL (R)      | SBDL          | (R)     | SIDL   | (R)   | SFBR   | (R)   |

| 10C           | SSTAT2 (R)    | SSTAT1        | (R)     | SSTAT0 | (R)   | DSTAT  | (R)   |

| 110           |               | DSA           | (R/W)   | •      |       | •      |       |

| 114           | CTEST3 (R)    | CTEST2        | (R)     | CTEST1 | (R/W) | CTEST0 | (R/W) |

| 118           | CTEST7 (R)    | CTEST6        | (R)     | CTEST5 | (R)   | CTEST4 | (R)   |

| 11C           |               | TEMP          | • (R/W) | •      |       | •      |       |

| 120           | LCRC (R/W     | () CTEST8     | (R/W)   | ISTAT  | (R/W) | DFIFO  | (R/W) |

| 124           | DCMD (R/W     | V)            |         | DBC    | (R/W) | •      |       |

| 128           |               | DNAI          | O (R/W) |        |       |        |       |

| 12C           |               | DSP           | (R/W)   |        |       |        |       |

| 130           | DSPS (R/W)    |               |         |        |       |        |       |

| 134           | SCRATCH (R/W) |               |         |        |       |        |       |

| 138           | DCNTL (R/W    | /) DWT        | (R/W)   | DIEN   | (R/W) | DMODE  | (R/W) |

| 13C           | ADDER (R)     |               |         |        |       |        |       |

| :             |               |               |         |        |       |        |       |

| 1FF           |               | RESE          | RVED    |        |       |        |       |

#### 3.11.1 SCSI Reset Register

Name:SCSI ResetAddress:Word 000, Byte 0Access:Write Only

A write to this register causes a directed reset to the SCSI subsystem.

#### 3.11.2 NCR 710 Internal Registers

Name:See table.Address:Words 100 to 13CAccess:See table.

Registers 100 to 13F are implemented inside the NCR53C710. See the NCR 53C710 Data Manual for the definitions of each field within each register.

| 712 I/O Subsystem ERS Rev 1.1 | Dwg No. A-A2263-66510-31 | Page 9 of 114 |

|-------------------------------|--------------------------|---------------|

|-------------------------------|--------------------------|---------------|

| 712 I/O Subsystem ERS Rev 1.1 | Dwg No. A-A2263-66510-31 | Page 10 of 114 |

|-------------------------------|--------------------------|----------------|

## 4 LAN

HEWLETT PACKARD

## 4.1 Introduction

The712 I/O Subsystem implements a local area network (LAN) to the 802.3/Ethernet standard. Ethernet is a 10 Mbit/s packet–switched serial interface employing Carrier Sense Multiple Access/ Collision Detection (CSMA/CD).

## 4.2 References

- Intel 82596CA High–Performance 32–Bit Local Area Network Coprocessor

- Intel 82596 User's Manual (Order Number: 296443–0001)

- Intel 82596 Data Sheet Supplement November 1989

- Intel Microcommunications Applications, vol. 1 & 2 (Order Number: 231658)

## **4.3 Nomenclature and Conventions**

Note than an Intel "word" is 16 bits, and a PA–RISC word is 32 bits. For both Intel and GSC, bits are numbered 31 (most significant) to 0 (least significant) from left to right.

## 4.4 Overview

The 712 built–in LAN is divided into two main physical blocks: the 82596 controller megacell and the 82C503 (or equivalent) interface. The controller is a megacell implementation of the stand– alone 82C596CA LAN controller from Intel. Please refer to the 82C596 documentation for detailed explanations of megacell functionality.

Lasi will typically be used with the 82C503, an intelligent LAN interface transceiver which provides both the MAU interface for conventional coaxial Ethernet and a direct interface to a twisted pair 10BASE-T network. This device will automatically detect whether a connection has been made to the MAU or twisted pair port and auto–configure to talk only to that port. No programmable interface will be provided in 712 to override the automatic selection. The automatic port selection capability will require the hub to be fully IEEE 802.3i–1990 compliant, providing the link integrity function as defined in the spec.

The LAN is also divided into two main functional blocks: the backplane interface to GSC and the frontplane interface to the network cable. The 82596 megacell depends on the Lasi GSC Interface to provide a proper backplane interface between the 32 bit multiplexed GSC bus and the non–multiplexed address and data busses on the megacell. The frontplane interface to the MAU and

10BASE-T connectors is provided by the 82C503. We advise the reader to consult the specification for this device for further information.

The 82596CA has a four channel DMA controller which allows it to communicate directly with the main memory via the Lasi internal bus and the GSC interface. The four channels are: CU (transmit header), TXD (transmit data), RU (receive header) and RXD (receive data). Following is a brief description of the shared memory model, repeated without permission from the Intel 82596 User's Manual, section 2.4.3. We strongly encourage the reader to consult this book for information about the chip:

"To off–load the CPU the 82596 implements a shared memory communication system with the host CPU. The 82596 and CPU do not communicate directly, but rather through a shared system memory 'mailbox.' This allows the CPU to place commands in the mailbox, activate **Channel Attention** to notify the 82596 of delivery, and return to its other processing chores. The 82596 checks its mailbox in response, retrieves and interprets the commands, and executes them without further CPU interaction. After the 82596 completes its tasks it places the results in system memory and updates the mailbox. Then the 82596 uses its **interrupt** line to notify the CPU of the presence of return mail..."

For normal DMA operations, the Lasi GSC interface arbitrates for GSC on the 82596 megacell's behalf, manages the address valid/ready handshake, and synchronizes the address and data buses via the transceivers.

## 4.5 Transaction Types

Apart from normal communication via shared memory, a limited number of operations directly to the megacell are available:

Note: all addresses are stated relative to the relocatable Lasi base address.

### 4.5.1 Channel Attention

To issue a Channel Attention to the 82596CA, do a word write to the LAN Channel Attention Register, at 008. No data is associated with this operation.

#### 4.5.2 Port Access

The 82596CA's "CPU Port" provides 4 functions:

- alternate System Configuration Pointer (SCP) address

- Dump command

- software reset

- self-test

Even though the megacell is in CA mode, the port accesses look like the part is in DX mode: the data needs to be on the lower 16 bits of the data bus for both port accesses. This change should be suffi-

| 712 I/O Subsystem ERS Rev 1.0 | Dwg No. A-A2263-66510-31 | Page 12 of 140 |

|-------------------------------|--------------------------|----------------|

|                               |                          |                |

cient to make the CA mode look like DX mode to software, maintaining software compatibility with previous 700 implementations.

The port is memory mapped. It is accessed via two consecutive 32–bit word writes to 004. This is due to the fact that only 16 bits are read at a time on this port when operating in big endian mode. See the 82596 User's Manual, pp. 5-18:5-20 for instructions on how to encode the data.

## 4.6 Reset

The 82596 has a hardware reset, CPU Port reset (see Port Access section above), and a software reset. In addition, software can control the lan bit in the IO\_RESET register at address offset 0x10C00C to force a hard reset of the LAN.

#### 4.6.1 Consequences

Resetting the megacell does NOT trigger self-test.

#### 4.6.1.1 Hardware Reset

The hardware reset causes the megacell to immediately cease all activity; the CU and RU become IDLE and clear all internal requests.

#### 4.6.1.2 CPU Port Reset

The CPU Port reset causes the megacell to immediately cease all activity and execute a software reset.

#### 4.6.1.3 Software Reset

The CU performs the following on recognition of a software reset:

- Terminates DMA activity.

- Writes zeros to the SCB Command word.

- Triggers a hardware reset.

#### 4.6.2 Protocol

#### 4.6.2.1 Hardware Reset

After power up, the 82596 requires a hardware reset. Lasi will automatically perform the reset as a result of the PON signal (for a primary Lasi) or the GSC RESETL signal (for a secondary Lasi), which by definition is asserted on power up. Code must wait for 10 system clocks and 5 transmit clocks (20 processor clocks + 0.5 microseconds for 10 Mbit/sec LAN) before doing a Channel Attention after a hardware reset. The LAN subsystem hardware will *not* check for the proper interval. **Code can cause a hardware reset by writing to 000.** This must be implemented by the Lasi GSC Interface block. A Channel Attention following a hardware reset will cause the 82596 to access the

SCP, which is located by default at 0x00FFFFF4 (or at an alternative address selected via the CPU Port). After Channel Attention the 82596 will read the sysbus byte and begin the initialization process.

#### 4.6.2.2 CPU Port Reset

For information on CPU Port operations, see Port Access section above. A *Channel Attention* following a *CPU Port reset* will cause the 82596 to access the SCP, which is located at 0x00FFFFF4 (or at an alternative address selected via the CPU Port). After Channel Attention the 82596 will read the sysbus byte and begin the initialization process. The CPU must wait for 10 system clocks and 5 transmit clocks (20 processor clocks + 0.5 microseconds for 10 Mbit/sec LAN) before issuing another Channel Attention to the 82596. The LAN subsystem hardware will *not* check for the proper interval.

#### 4.6.2.3 Software Reset

A software reset is available through bit 7 of the control command word in the SCB. It can be used after the 82596 has been initialized and has the ISCP and SCP addresses.

### 4.7 Interrupts

Lasi provides a uniform interface for all I/O interrupts, including LAN (see interrupt section of this document). Interrupts are generated by one or more of the following events (from page 3–46 of the User's Manual):

- Execution of a Command Block with its *I* bit set (*CX* interrupt).

- Reception of a frame (*RU* interrupt).

- The CU becoming not active (*CNA* interrupt).

- The RU becoming not ready (*RNR* interrupt).

For more information about what these actually mean, consult section 5.3 of the User's Manual.

For compatibility with existing drivers, LASI assumes that the interrupt line driven by the megacell will be active low. It follows that the interrupt bit in the SYSBUS byte should be a 1. Also, since the default for the interrupt line is active high after reset, interrupts should be disabled via the LASI interrupt mask register during reset. They should be enabled only after the LAN has a chance to read the SYSBUS byte in response to a CA. Otherwise, a spurious interrupt may be generated.

## 4.8 Programming Considerations

Note: Several errata have been discovered in the Intel chip and documentation. Some are mentioned below, but firmware, driver and software writers are strongly encouraged to consult the errata sheet.

Note: the 82596 megacell will be utilized in CA mode within Lasi, as opposed to the DX mode operation for 720/730/750. Utilization of CA mode was chosen to allow access to the data burst mode supported by the 82596 in CA mode only.

### 4.8.1 Endian Mode

The 82596 will be set to operate in big endian mode to be compatible with GSC. Programmers should take care to consult the big endian sections of the various references.

## 4.8.2 Bus Size

The Lasi GSC Interface provides a 32 bit data bus to the LAN controller.

### 4.8.3 System Configuration Pointer

The SCP defaults to 0x00FFFFF4. If this is unacceptable given memory configuration and other system parameters, firmware/software must write an acceptable value to the LAN Port Select (see above) between reset and first Channel Attention. The reader is reminded that alternate SCP addresses must be divisible by 16. In addition, *the SCP must reside in system memory*. The Intel book suggests putting the SCP in ROM, but in the 712, the ROM is on the Flash EPROM bus, and this bus is only readable by the host. All data structures must reside in main memory.

Please make sure that any bits marked "x" in the SCP description are set to 0. Intel informs us that the chip will not work otherwise.

As always, see the manual for more information.

## 4.8.4 Sysbus Byte

The sysbus byte must be located at 0x00FFFFF7, or at location n+1 if an alternative SCP is used. Following is a discussion of the sysbus configuration byte. Please refer to section 5.4 of the manual.

#### 4.8.4.1 Mode

Presumably, the 82596CA will be used in the *linear* mode. Set the bits accordingly.

#### 4.8.4.2 Bus Throttle and Arbitration

In brief, this is how arbitration works: When the LAN needs the bus, it pulls its HOLD line. Based on the core I/O priority scheme, Lasi arbitrates for GSC on the LAN's behalf, then grants it the bus by asserting HLDA. The 82596 then has the bus for as long as it wants, which in general should be less than 5  $\mu$ s.

By default, we will not use the bus throttle features. To do this, **set the TRG bit of the sysbus byte to 1** for external bus release triggering. The external trigger is hard wired inactive. These two measures in tandem with the Lasi arbitration mechanism allow the 596 to have the bus for as long as it needs to finish all pending work. However, if during system testing it is discovered that the 596 hangs onto the bus to the extent that it degrades system performance, it would be desirable to have an easy (i.e. run–time) way of (1) enabling the internal bus throttle trigger by setting the TRG bit to 0 and (2) configuring the 596 throttle registers.

#### 4.8.4.3 Locked Cycles

The LOCK bit of the sysbus byte should be set to 0 to enable "semaphore" operations on UP-DATE\_ERR\_CNTRS and RCV\_RBD\_PREFETCH.

#### 4.8.4.4 Interrupt Pin Polarity

The INT bit of the sysbus byte should be set to 1 to force the INT pin to be active low.

#### 4.8.4.5 Channel Switch Algorithm

Intel informs us that the CSW bit of the sysbus byte must be set to 1 for correct chip operation.

#### 4.8.5 Performance Considerations

#### 4.8.5.1 FIFO Vector

Although the 82596CA has large FIFOs, 128 bytes on receive and 64 on transmit, certain system configurations may impose long bus access latencies on the LAN. The FIFO has a programmable threshold. If the FIFO *vector* (note this is *not* the same as the threshold *value*) is set too high, the megacell will frequently request the bus, thus causing inefficiency due to arbitration overhead. Refer to section 7.3, *Setting the FIFO Thresholds*, in the User's Manual. If it is set too low, the FIFO may overrun or underrun before getting the bus. It is probable that some tuning will be required to fully optimize performance.

#### 4.8.5.2 Memory Organization

In general, simplified, linear memory structures aligned on 4 byte boundaries, and larger size for data buffers, will tend to help LAN hardware performance, but at a cost to efficient memory utilization.

## 4.9 Station Nodal Address

A permanent copy of the LAN Station Nodal Address is kept in Flash EPROM.

## 4.10 LAN Memory Map

The memory map below does not include the address block referenced by the System Configuration Pointer (SCP).

All addresses in the memory map are Write Only, are are specified relative to the relocatable Lasi base address. To read internal state, execute the Dump command.

|               | 31              | Bit Numberi | ng     |        | 0 |

|---------------|-----------------|-------------|--------|--------|---|

| Address (Hex) | Byte 0          | Byte 1      | Byte 2 | Byte 3 |   |

| 000           | Reset (no data) |             |        |        |   |

#### HEWLETT PACKARD

| 004 | CPU PORT_L Access – see sec. 5.4 of the 82596 User Manual |

|-----|-----------------------------------------------------------|

| 008 | Channel Attention (no data)                               |

| 712 I/O Subsystem ERS Rev 1.0 | Dwg No. A-A2263-66510-31 | Page 17 of 140 |

|-------------------------------|--------------------------|----------------|

|-------------------------------|--------------------------|----------------|

| 712 I/O Subsystem ERS Rev 1.0 | Dwg No. A-A2263-66510-31 | Page 18 of 140 |

|-------------------------------|--------------------------|----------------|

## **5 PARALLEL INTERFACE**

## 5.1 Introduction

The Parallel Interface is an 8 bit parallel, synchronous interface commonly used for printers. The 712 hardware implementation has bidirectional capabilities compatible with PS2 standards, also known to the world as Centronics(tm). The 712 hardware is also capable of interfacing to BiTronics type printers which transmit status information back to the workstation. The Apollo CP300 (alias Tektronics 4693D) raster copier (printer) is also supported. The HP Scanjet parallel port interface is NOT supported on the 712 and cannot be supported, even through software handshaking.

This chapter is divided into two sections: the first covers the parallel port slave interface and the second describes the DMA controller used by the parallel port.

## 5.2 Overview

The PS2 and AT compatible features are controlled through Lasi. Lasi emulates most of the functionality of the WD16C522 parallel to provide a 720/730 compatible device driver/receiver interface. Handshaking functionality required by CP300 products is provided by special hardware built into Lasi. Lasi drives and receives all signals to/from the parallel port connector without intermediate buffers.

### 5.3 Features

- Supports outbound host DMA

- Bidirectional non–DMA interface

- Supports Bitronics interface through software.

- Supports Apollo CP300 (aka Tektronics 4693) raster copier.

- 25-pin female DB25 connector (same as IBM PS/2)

- Recognizes both NACK and BUSY handshakes, independently or together

- Pull-up resistors on all lines

## 5.4 Addressing

All addresses within this chapter are offsets from the base address for each 4K block. The Parallel slave registers, the DMA registers, and the DMA reset register each have a separate 4K block. The

| 712 I/O Subgration EDS Day 1.0 | $D_{WG} N_{0} A A 2262 66510 21$ | Decc. 10 of 115 |

|--------------------------------|----------------------------------|-----------------|

| 712 I/O Subsystem ERS Rev 1.0  | Dwg No. A-A2263-66510-31         | Page 19 01 115  |

abbreviations listed in the following table show the base address to be used for a given register. Please note that the 4K base addresses listed in the table need to be OR'd with the Lasi Base Address determined by the SPACE[1:0] bits.

| Abbreviation | 4K Base Address |

|--------------|-----------------|

| dma          | 10_1000         |

| slv          | 10_2000         |

| drst         | 10_3000         |

Addresses in this document are always byte addresses. All addresses should be accessed with byte transactions from the host. This allows backwards compatability with previous interfaces which supported only byte accesses and also prevents unintended register modification. Lasi's parallel interface will properly handle 16-bit and 32-bit writes and reads but, because sparse decoding is used, unintended actions could result.

For example, a 32-bit write to address slv+0x800 would put byte 0 data out on the parallel data lines (and potentially start a full handshake depending on the mode selected), write byte 1 data to the status register (this would be ignored), write byte 2 data to the Parallel Device Control register, and byte 3 data would be ignored. However, a 32-bit write to dma+0x400 would put byte 1 data into the Current Count High Byte register as expected, but would also write to three other registers because many registers have multiple addresses. In this case, byte 0 data would be written to the Current Address register, byte 2 data would be written to the DMA Interrupt Logging register, and byte 3 data would be written to the Current Address High Page register.

### 5.5 Power Up Reset

The following conditions are set during power up reset:

- All parallel interface state machine controllers in Lasi are reset.

- NSTB is High.

- NAFD (alias WRnRD, WR/nRd) is High.

- NINIT (alias NRESET, nRESET) is Low.

- NSLIN (alias NSLCT\_IN, NSLCTIN) is Low.

- All Parallel Port Interrupts will be disabled.

- TDC1 is loaded with 1 μs count value.

## 5.6 Quick Reference for Parallel Slave Registers

|                            | Bit            | 7                               | 6                    | 5       | 4            | 3            | 2     | 1       | 0      |

|----------------------------|----------------|---------------------------------|----------------------|---------|--------------|--------------|-------|---------|--------|

| Register<br>Abrev.<br>Name | Bit Val-<br>ue | \$80                            | \$40                 | \$20    | \$10         | \$8          | \$4   | \$2     | \$1    |

|                            | Address        |                                 |                      |         |              |              |       |         |        |

| ParReset                   | slv+000        |                                 |                      | Reset ( | data value   | e ignored)   | ).    |         |        |

| ParData                    | slv+800        |                                 | DATA                 |         |              |              |       |         |        |

| ParStatus                  | slv+801        | Nbusy                           | Nack                 | pe      | slct         | Nerr         | Nint  | 1       | 1      |

| ParDevCtl                  | slv+802        | 1                               | 1                    | NwrRd   | IrqEnb       | NSlin        | Ninit | Autofd  | Strobe |

|                            | slv+803        |                                 | Not Used (undefined) |         |              |              |       |         |        |

| ModeCtl                    | slv+804        | Mode[2]                         | Mode[1]              | Mode[0] | Biden        | fNstb        | 0     | 0       | 0      |

| IECtlStat                  | slv+805        | dmaInt                          | 0                    | NbsyInt | Nack-<br>Int | ack-<br>Nbsy | peInt | slctInt | errInt |

| TDC0                       | slv+806        | Timing Delay Value 0 (obsolete) |                      |         |              |              |       |         |        |

| TDC1                       | slv+807        |                                 |                      | Timi    | ng Delay     | Value 1      |       |         |        |

## 5.7 Slave Register Descriptions

### 5.7.1 Directed Master Reset (Address slv+0x000)

| Bit<br>Field | Name  | Write Effect                                                                                                                                                                                                                                                                                                               | Value on Read     |

|--------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 7–0          | Reset | This has the same effect on the Parallel<br>Interface as the power up reset described<br>before except that the NSTB, NAFD, NI-<br>NIT, and NSLIN lines are not affected.<br>Software must initialize those outputs by<br>writing the appropriate bits in ParDevCtl<br>(slv+0x802) after a directed reset is in-<br>voked. | May be any value. |

#### 5.7.2 Write/Read Data (Address slv+0x800)

| Bit<br>Field | Name    | Write Effect                                                                                                                                                                                                                                                                                                                                                     | Value on Read                                                                                                                                                         |

|--------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0          | ParData | <ul> <li>Write data direct to parallel port according to handshake mode selected. There are two ways of setting the port to write mode:</li> <li>1) Set the direction bit, Biden (slv+0x804 bit 4), to 0.</li> <li>2) Set slv+0x804 bit 4 to 1 and slv+0x802 bit 5 to 0.</li> <li>Note: Write to this address only when in handshake Mode 0, 1, or 2.</li> </ul> | Read data direct from parallel port. Biden<br>(slv+0x804 bit 4) must = 1 and NwrRd<br>(slv+0x802 bit 5) must = 1.<br>Note: Read used only when in handshake<br>Mode 0 |

NOTE:

Writes to this register while DMA is in progress will be ignored, but reads will work properly.

#### 5.7.3 Parallel Port Status (Address slv+0x801)

| Bit<br>Field | Name  | Write Effect | Value on Read                                    |

|--------------|-------|--------------|--------------------------------------------------|

| 7            | Nbusy | Ignored.     | returns 0 if the BUSY signal is asserted (high). |

| 6            | Nack  | Ignored.     | returns 0 if the NACK signal is asserted (low).  |

| 5            | pe    | Ignored.     | returns 1 if the PE signal is asserted (high).   |

| 4            | slct  | Ignored.     | returns 1 if the SLCT signal is asserted (high). |

| 3            | error | Ignored.     | returns 0 if the NERR signal is asserted (low).  |

| 2            | NINT  | Ignored.     | Returns 1.                                       |

| 1            |       | Ignored.     | Returns 1.                                       |

| 0            |       | Ignored.     | Returns 1.                                       |

Bit 2 was defined as NINT in the 720/730 documentation. With 720/730 this bit returns a 0 if NACK had a low to high (trailing edge) transition, and reading the status register will set this bit to 1. However, on 720/730 products this bit cannot generate a system interrupt to the processor. A complete set of interrupt choices, including a NACK interrupt with this functionality, is available in the "IE Control/Interrupt Status" register (Byte Address slv+0x805), so this function is redundant. Furthermore, the "IE Control/ Interrupt Status" can be used to generate a system interrupt.

| Bit<br>Field | Name   | Write Effect                                                                                                                                                            | Value on Read                                                      |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 7,6          |        | Ignored.                                                                                                                                                                | Returns 1 for both bits.                                           |

| 5            | NwrRd  | Direction control. Only significant if bi-<br>den = 1 (see Byte Address 4, bit 4). If 1,<br>direction is "input from device". If 0,<br>direction is "output to device". | Returns 1.                                                         |

| 4            | IrqEnb | Ignored. (See note under status register definition.)                                                                                                                   | Returns 0.                                                         |

| 3            | NSlin  | If 1, NSLIN = H. If 0, NSLIN = L.                                                                                                                                       | If signal at connector is high, returns 1.<br>Otherwise returns 0. |

| 2            | Ninit  | If 1, NINIT = H. If 0, NINIT = L.                                                                                                                                       | If signal at connector is high, returns 1.<br>Otherwise returns 0. |

| 1            | Autofd | If 1, NAFD = L. If 0, NAFD = H.                                                                                                                                         | If signal at connector is low, returns 1.                          |

| 0            | Strobe | If 1, NSTB = L. If 0, NSTB = H                                                                                                                                          | Otherwise returns 0.                                               |

#### 5.7.4 Parallel Device Control (Address slv+0x802)

With ASP, this register exists on a separate WD16C522 part. When ASP is in mode 1, 2,3, or 4, it writes to the WD part to change NSTB. This write forces NwrRd to 0, IrqEnb to 0, Nslin to 0, Ninit to 1, Nafd to 1. At the end of the transfer, Nstb is 1. With Lasi, NwrRd, IrqEnb, Nslin, Ninit, and Nafd will not change if an automatic handshake mode is being used: their value will change only by writing this register. Nstb will be dependent on the mode selected in the Mode Control register. If the mode is 1, 2, or 4, Nstb will be high when no transfer is in progress. If mode 0 is used, Nstb will be dependent on this register. Care should be taken to insure NSTB=H (bit 0=0) when the mode value is changed, so no stray pulses occur on NSTB.

### 5.7.5 Mode Control (Address slv+0x804)

Hardware supports both DMA and non–DMA transfers for automatic handshake modes 1, 2, and 4. Mode 3—the Scanjet automatic handshake mode—is not implemented in Lasi.

CAUTION: Changing modes before a previous parallel data transaction is complete may cause unpredictable results. Software must always make sure previous transactions are complete before changing modes.

| Bit<br>Field | Name  | Write Effect                                                                                                                                                                                                                                                                                                                | Value on Read               |  |

|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| 7–5          | Mode  | Sets current mode. See the next table for mode encodings.                                                                                                                                                                                                                                                                   |                             |  |

| 4            | Biden | Bidirectional enable. If 1, data buffers<br>will accept data from device. If 0, data<br>buffers will drive data to the device.                                                                                                                                                                                              |                             |  |

| 3            | Fstb  | Force NSTB pulse. When 1, forces<br>NSTB pulse to be low for the pro-<br>grammed delay period, i.e. NSTB H to L<br>transition is not conditional on BUSY=H.<br>Prevents deadlock condition for devices<br>which only return BUSY=1 when NSTB<br>makes a L to H transition (such as the<br>CP300 device in non-stream mode). | Returns value written       |  |

| 2–0          |       | Ignored.                                                                                                                                                                                                                                                                                                                    | May return either a 0 or 1. |  |

| Mode Reg Bits |       |       |                |                                                                                                                                                                                                                                                        |

|---------------|-------|-------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7         | Bit 6 | Bit 5 | Handshake Mode | Mode Description                                                                                                                                                                                                                                       |

| 0             | 0     | 0     | Mode 0         | No automatic hardware handshake.<br>Handshaking is under software con-<br>trol.                                                                                                                                                                        |

| 0             | 0     | 1     | Mode 1         | NACK pulse with not BUSY hand-<br>shake. Handshake is complete if<br>NACK pulse has completed and then<br>BUSY=L. DMA or non–DMA trans-<br>fers are allowed.                                                                                           |

| 0             | 1     | 0     | Mode 2         | BUSY only handshake                                                                                                                                                                                                                                    |

| 0             | 1     | 1     | Mode 3         | Reserved                                                                                                                                                                                                                                               |

| 1             | 0     | 0     | Mode 4         | Stream mode. Automatic NSTB gen-<br>eration with no NACK or BUSY<br>handshakes. Hardware will make the<br>data setup, strobe duration, and data<br>hold times the same as determined by<br>the delay value programmed via<br>TDC1 (address slv+0x807). |

| 1             | 0     | 1     | Mode 0         | see above                                                                                                                                                                                                                                              |

| 1             | 1     | 0     | Mode 0         | see above                                                                                                                                                                                                                                              |

| 1             | 1     | 1     | Mode 0         | see above                                                                                                                                                                                                                                              |

# 5.7.6 IE Control/Interrupt Status (Address slv+0x805)

| Bit<br>Field | Name                  | Write Effect (Interrupt Enables)                                                                                        | Read (Interrupt Requests)                                                                                                                    |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7            | DMA<br>done           | Enable interrupts for when DMA com-<br>pletes its block transfer. (Interrupt when the<br>whole pipeline is empty.)      | DMA done has made a 0 to 1 transition, so<br>DMA has completed its block transfer.<br>This bit is cleared only by writing a zero<br>into it. |

| 6            |                       | No effect.                                                                                                              | Returns 0.                                                                                                                                   |

| 5            | Nbusy<br>Intr         | Enable interrupts on BUSY trailing edge H to L transition.                                                              | Busy H to L transition (not busy). This bit is cleared only by writing a zero into it.                                                       |

| 4            | Nack<br>Intr          | Enable interrupts on NACK trailing edge LNACK L to H transition occurred. This<br>is cleared by writing a zero into it. |                                                                                                                                              |

| 3            | ack-<br>Nbusy<br>Intr | Enable interrupts when NACK transitions from L to H and BUSY = L (not busy).                                            | NACK L to H transition occurred and<br>BUSY = L. This bit is cleared only by writ-<br>ing a zero into it.                                    |

| 2            | PE Intr               | Enable interrupts on any PE transition.                                                                                 | The PE line has made any transition. This bit is cleared only by writing a zero into it.                                                     |

| 1            | Select<br>Intr        | Enable interrupts on any SLCT transition.                                                                               | The SLCT line has made any transition.<br>This bit is cleared only by writing a zero<br>into it.                                             |

| 0            | Error<br>Intr         | Enable interrupts on any NERR transition.                                                                               | The NERR line has made any transition.<br>This bit is cleared only by writing a zero<br>into it.                                             |

Logic exists to prevent losing interrupts. The following sequence demonstrates the interrupt logic behavior:

- 1. Two or more bits of this register are set.

- 2. Two or more interrupts which are enabled in this register become pending.

- 3. The enabled Lasi global parallel interrupt register bit becomes active causing the interrupt to be serviced by the host.

- 4. The host reads this register, clears the Lasi global parallel interrupt bit, and then chooses to clear only one of the pending interrupts by writing that bit to zero in this register and writing one(s) for the other pending interrupt bit(s).

- 5. Another interrupt edge for the other pending and enabled interrupt(s) will be generated to the global parallel pending interrupt bit in Lasi immediately following the write to this register.

Also, if an interrupt was pending but not enabled, and then the host enables that pending interrupt, an interrupt edge will be sent to the Lasi global parallel interrupt register bit.

# 5.7.7 Timing Delay Counter 0 (Address slv+0x806)

This register provides backwards compatibility with products using the Asp chip. On these products, a bug fix required loading this register with a value based on the bus speed. For compatibility

| 712 I/O Subsystem ERS Rev 1.0 | Dwg No. A-A2263-66510-31 | Page 25 of 115 |

|-------------------------------|--------------------------|----------------|

|                               |                          |                |

with kernel I/O drivers written for these systems, this register exists in the register map, but doesn't have any function.

| Bit<br>Field | Name | Write Effect | Value on Read         |

|--------------|------|--------------|-----------------------|

| 7–0          | TDC0 | Ignored.     | May return any value. |

# 5.7.8 Timing Delay Counter 1 (Address slv+0x807)

|         | T1         | T2         | ТЗ         |          |

|---------|------------|------------|------------|----------|

|         |            |            |            |          |

| NSTB    |            |            |            |          |

|         |            |            |            |          |

|         |            |            |            |          |

| DATA —— | Valid Data | Valid Data | Valid Data | X        |

|         |            |            |            | <u> </u> |

#### Figure 2. Parallel Data Timing

| Bit<br>Field | Name | Write Effect                                                                                                                                                                                                                                | Value on Read          |  |

|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| 7–0          | TDC1 | A count value which establishes the mini-<br>mum data setup (T1) and NSTB pulse<br>(T2) times. Also establishes the data<br>hold time (T3) when in mode 4 (stream<br>mode). The same count value is used for<br>the T1, T2, and T3 periods. | Returns value written. |  |

|              |      | Note: The NSTB pulse will be low for<br>the delay time programmed or the<br>time it takes for BUSY to become<br>true, whichever comes last.                                                                                                 |                        |  |

To compute the count value for this register, use the following formula:

<count\_value> = (<desired\_delay> - 200ns) / 50 ns

The "standard" for desired delay is typically equal to or greater than  $1 \ge 10E-6$  second (1  $\mu$ s). However, other values may be chosen depending on peripheral/cable restrictions. Be sure to round up to the next higher integer value to ensure that the timing is not under the minimum delay time required. Some examples follow:

> calculated value = 8.6 ... round up to 9 calculated value = 8.3 ... round up to 9 calculated value = 8.0 ... use 8

At power up, the register will have a value necessary to insure a delay of at least 1  $\mu$ s for each period (T1, T2, and T3).

# 5.8 Parallel Port DMA Controller

The 712's parallel port DMA controller emulates an EISA DMA controller by providing the same register map and counter behavior. To simplify system verification and minimize area, the 712's parallel port DMA reads one 32–bit word from memory at a time and then releases the bus.

|                  | DMA Controller Register Map |                 |                                    |  |  |

|------------------|-----------------------------|-----------------|------------------------------------|--|--|

| Address          | Туре                        | Size<br>(Bytes) | Description                        |  |  |

| <i>drst</i> +000 | write only                  | 1               | DMA Reset Register                 |  |  |

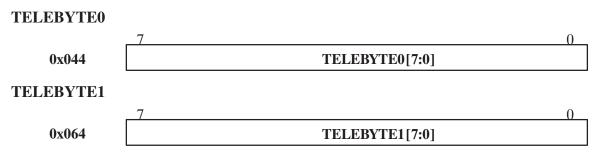

| dma+000          | read/write                  | 1               | Current Address Register           |  |  |